# **STLC7549**

# STEREO AUDIO/MODEM/TELEPHONY CODEC

#### ADVANCE DATA

STEREO AUDIO CODEC WITH CD QUALITY NOISE AND DISTORTION

SGS-THOMSON

- ADC AND DAC SAMPLING RATES UP TO 48kHz

- 16-BIT RESOLUTION

- > 85dB DYNAMIC RANGE

- QUADRAPHONIC MODE FOR SURROUND SOUND APPLICATION (STEREO AUDIO CODEC PLUS BOTH MONOPHONIC CODECS)

- MONOPHONIC CODEC FOR MODEM APPLI-CATIONS

- ADC AND DAC SAMPLING RATES UP TO 44.1kHz

- 16-BIT RESOLUTION

- > 90dB DYNAMIC RANGE (MODEM MODE)

- V.34 MODEM PERFORMANCE CAPABILITY

- SECOND MONOPHONIC CODEC FOR LOCAL HANDSET (or 2<sup>nd</sup> MODEM) APPLICATIONS

- ADC AND DAC SAMPLING RATES

- UP TO 44.1kHz

- 16-BIT RESOLUTION

- > 85dB DYNAMIC RANGE (MODEM MODE)

- EXTENSIVE AUDIO SWITCHING AND GAIN CONTROLS FOR AUDIO ROUTING

- A SUPERSET FEATURE LIST OF SOUND-BLASTER PRO AND MPC-2 SPECIFICATIONS

- 3 STEREO LINE LEVEL INPUTS (LINE IN, CDROM, AUX)

- 2 MONOPHONIC MICROPHONE INPUTS (DESKTOP AND HEADSET)

- 2 PAIR OF STEREO OUTPUTS (MAIN AND AUXILLARY)

- MONO INPUT AND MONOPHONIC OUTPUT

- PROGRAMMABLE GAIN/ATTENUATION/ MUTE BLOCKS ON ALL INPUTS AND OUTPUTS

- MODEM CODEC HAS GAIN/ATTENUATION BLOCKS

- INPUTS AND OUTPUTS CAN OPERATE IN A BALANCED OR UNBALANCED CON-FIGURATION

- DAC OUTPUT CAN OPTIONALLY BE USED AS REAR CHANNEL SOUND EFFECTS FOR GAMES

- 2<sup>nd</sup> MODEM CODEC HAS GAIN/ATTENUATION/ MUTE BLOCKS ON INPUT AND OUTPUT

- ADC CAN SELECT HANDSET MOUTHPIECE OR DESKTOP/HEADSET MICROPHONE

- DAC OUTPUT CAN OPTIONALLY BE USED AS REAR CHANNEL SOUND EFFECTS FOR GAMES

- DAC OUTPUT CAN OPTIONALLY BE USED TO DRIVE THE HEADSET EARPIECE

- THIS CODEC CAN ALSO BE USED FOR A SECOND MODEM PORT

- CONTROL PINS TO CONTROL LINE OUT ATTENUATORS BY PUSHBUTTONS UP/DOWN/MUTE

- CONTROL PIN TO CONTROL LINE OUT AT-TENUATORS BY A DC-VOLTAGE POTENTI-OMETER

- GENERAL PURPOSE DIGITAL I/O LINES FOR CONTROL OF MISCELLANEOUS TELE-PHONE CIRCUITS

- EXTENSIVE POWER DOWN OPTIONS WITH LOW-POWER AUDIO LOOPTHRU MODE

- DUAL SYNCHRONOUS SERIAL PORTS WITH 64 BITS PER FRAME

- DIGITAL POWER SUPPLY OF 3.3V TO 5.0V

- ANALOG POWER SUPPLY OF 5V

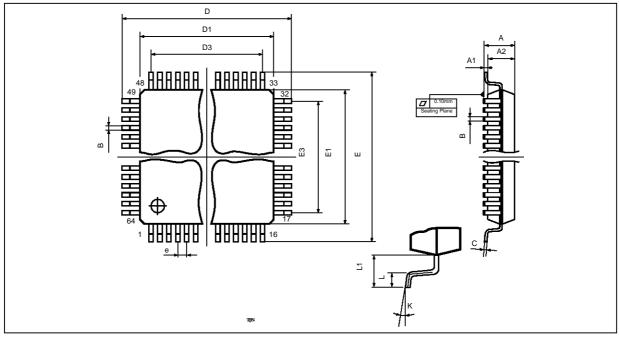

- AVAILABLE IN 64 PIN TQFP PACKAGE

#### DESCRIPTION

The STLC7549 codec is a single chip multimedia codec that contains multiple 16-bit sigma-delta codecs and a wide assortment of audio switching and gain controls.

April 1996

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

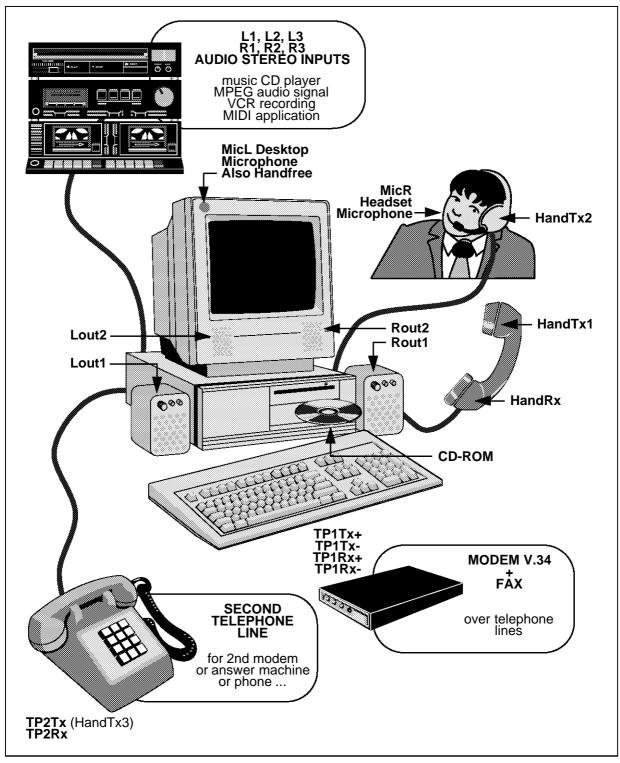

#### **MULTIMEDIA WORLD**

### **STLC7549**

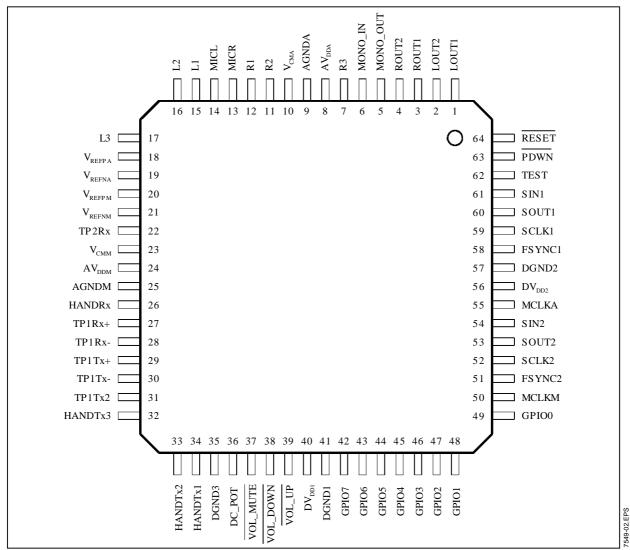

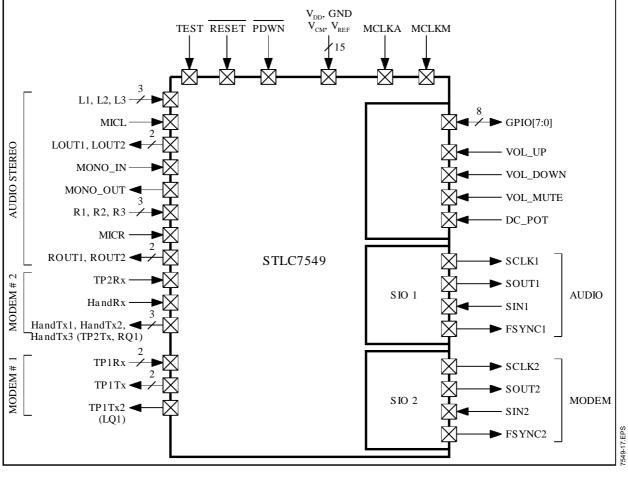

#### **PIN CONNECTIONS**

#### **PIN DESCRIPTION**

| Pin N°           | Symbol                                                                                                                                                                                                                                                                                        | Туре     | Function                                                                                                                                                                                                                                                      |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| POWER            | SUPPLY (9 pins                                                                                                                                                                                                                                                                                | ) (see N | lotes 1 and 2)                                                                                                                                                                                                                                                |  |  |

| 8                | AVdda                                                                                                                                                                                                                                                                                         | I        | Analog V <sub>DD</sub> Supply. This pin is the positive analog power supply voltage (4.75V to 5.25V) for the DAC and the ADC audio section. The voltage on these pins must be higher or equal to the voltage of the Digital power supply (DV <sub>DD</sub> ). |  |  |

| 24               | A AV <sub>DDM</sub> I Analog V <sub>DD</sub> Supply. This pin is the positive analog power supply voltage (4.75)<br>5.25V) for the DAC and the ADC modem and telephony section. The voltage on<br>pin must be higher or equal to the voltage of the Digital power supply (DV <sub>DD</sub> ). |          |                                                                                                                                                                                                                                                               |  |  |

| 40,56            | DV <sub>DD1</sub> , DV <sub>DD2</sub>                                                                                                                                                                                                                                                         | I        | Digital $V_{DD}$ Supply. This pin is the positive digital power supply (3.15V to 5.25V).                                                                                                                                                                      |  |  |

| 9                | AGNDA                                                                                                                                                                                                                                                                                         | I        | Analog Ground. This pin is the ground return of the analog DAC (ADC) audio section.                                                                                                                                                                           |  |  |

| 25               | AGNDM                                                                                                                                                                                                                                                                                         | I        | Analog Ground. This pin is the ground return of the analog DAC (ADC) modem and telephony section.                                                                                                                                                             |  |  |

| 41,<br>57,<br>35 | DGND1,<br>DGND2,<br>DGND3                                                                                                                                                                                                                                                                     | I        | Digital Ground. These pins are the ground return of the digital section.                                                                                                                                                                                      |  |  |

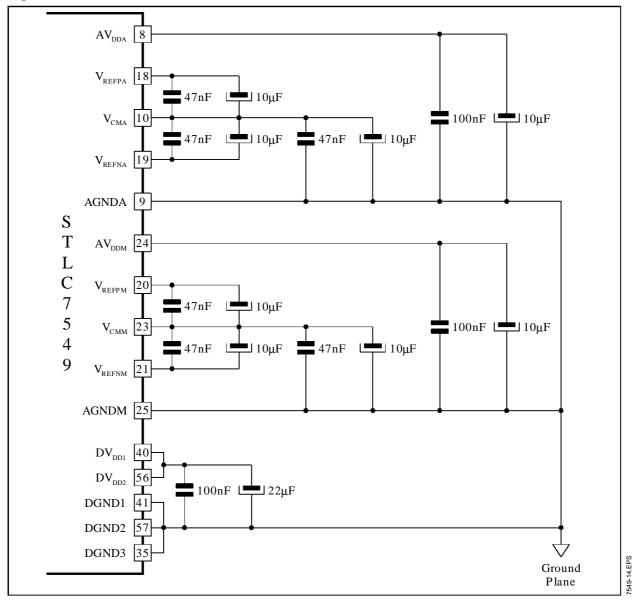

Notes: 1. To obtain published performance, the analog V<sub>DD</sub> and digital V<sub>DD</sub> should be decoupled with respect to analog ground and digital ground, respectively. The decoupling is intended to isolate digital noise from the analog section; decoupling capacitors should be as close as possible to the respective analog and digital supply pins (refer to Figure 11).

2. All the ground pins must be tied together. In the following section, the ground and supply pins are referred to as GND and V\_DD, respectively. 3/30

# PIN DESCRIPTION (continued)

| Pin N°  | Symbol             | Туре    | Function                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STEREC  | AUDIO CODEC        | (17 pin | s)                                                                                                                                                                                                                                                                                                                                                                                       |

| Voltage | Reference          |         |                                                                                                                                                                                                                                                                                                                                                                                          |

| 18      | Vrefpa             | 0       | Stereo Audio DAC and ADC Positive Reference Voltage Output. This pin provides the Positive Reference Voltage used by the 16-bit stereo audio converters. The reference voltage, $V_{REFA}$ , is the voltage difference between the $V_{REFPA}$ and $V_{REFNA}$ outputs. $V_{REFPA}$ should be externally decoupled with respect to $V_{CMA}$ . $V_{REFA} = V_{REFPA} - V_{REFNA}$ .      |

| 19      | V <sub>REFNA</sub> | 0       | Stereo Audio DAC and ADC Negative Reference Voltage Output. This pin provides the Negative Reference Voltage used by the 16-bit stereo audio converters, and should be externally decoupled with respect to V <sub>CMA</sub> .                                                                                                                                                           |

| 10      | Vcma               | 0       | Audio Common Mode Voltage Output. This output pin is the common mode voltage (AV <sub>DDA</sub> -AGNDA)/2. This output must be decoupled with respect to AGNDA.                                                                                                                                                                                                                          |

| Analog  | Inputs             |         |                                                                                                                                                                                                                                                                                                                                                                                          |

| 15      | L1                 | I       | Left Line Input #1. Left analog input #1. Full scale input, with no gain, is $1V_{RMS}$ , centered at $V_{CMA}$ .                                                                                                                                                                                                                                                                        |

| 16      | L2                 | I       | Left Line Input #2. Left analog input #2. Full scale input, with no gain, is $1V_{\text{RMS}}$ , centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                          |

| 17      | L3                 | I       | Left Line Input #3. Left analog input #3. Full scale input, with no gain, is $1V_{RMS}$ , centered at $V_{CMA}$ .                                                                                                                                                                                                                                                                        |

| 14      | MICL               | I       | Left Microphone Input. Microphone input for the left MIC channel, centered at $V_{CMA}$ . This signal can be either $1V_{RMS}$ or $0.1V_{RMS}$ depending on the preamp gain.                                                                                                                                                                                                             |

| 12      | R1                 | Ι       | Right Line Input #1. Right analog input #1. Full scale input, with no gain, is $1V_{\text{RMS}}$ , centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                        |

| 11      | R2                 | I       | Right Line Input #2. Right analog input #2. Full scale input, with no gain, is $1V_{\text{RMS}}$ , centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                        |

| 7       | R3                 | I       | Right Line Input #3. Right analog input #3. Full scale input, with no gain, is $1V_{\text{RMS}}$ , centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                        |

| 13      | MICR               | I       | Right Microphone Input. Microphone input for the right MIC channel, centered at $V_{CMA}$ . This signal can be either $1V_{RMS}$ or $0.1V_{RMS}$ depending on the preamp gain.                                                                                                                                                                                                           |

| 6       | MONO_IN            | I       | Monophonic input , centered at $V_{CMA}$ . This signal can be $1V_{RMS}$ . This is a general purpose mono analog input that is normally used to mix the typical "beeper" signal on most computers into the audio system.                                                                                                                                                                 |

| Analog  | Outputs            |         |                                                                                                                                                                                                                                                                                                                                                                                          |

| 1       | LOUT1              | 0       | Left Channel Output #1. Left channel analog output. Maximum signal is $1V_{\text{RMS}}$ centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                                   |

| 2       | LOUT2              | 0       | Left Channel Output #2. Left channel analog output. Maximum signal is $1V_{\text{RMS}}$ centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                                   |

| 3       | ROUT1              | 0       | Right Channel Output #1. Right channel analog output. Maximum signal is $1V_{\text{RMS}}$ centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                                 |

| 4       | ROUT2              | 0       | Right Channel Output #2. Right channel analog output. Maximum signal is $1V_{\text{RMS}}$ centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                                                                 |

| 5       | MONO_OUT           | 0       | Mono Output. This output is a summed analog output from the left and right and Mono input channels. Maximum signal is $1V_{\text{RMS}}$ centered at $V_{\text{CMA}}$ .                                                                                                                                                                                                                   |

| NODEM   | AND TELEPHO        | NY COE  | DEC (13 pins)                                                                                                                                                                                                                                                                                                                                                                            |

| 20      | Vrefpm             | 0       | Modem and Telephony DAC and ADC Positive Reference Voltage Output. This pin provides the Positive Reference Voltage used by the 16-bit modem converters and the 16-bits telephony converters. The reference voltage, V <sub>REFM</sub> , is the voltage difference between the V <sub>REFPM</sub> and V <sub>REFNM</sub> outputs. V <sub>REFPM</sub> should be externally decoupled with |

21

VREFNM

O

Modem and Telephony Common Mode Voltage used by the 16-bit modem converters and the provides the Positive Reference voltage, VREFM, is the voltage difference between the VREFPM and VREFNM outputs. VREFPM should be externally decoupled with respect to VCMM. VREFM = VREFPM - VREFNM.

21

VREFNM

O

Modem and Telephony DAC and ADC Negative Reference Voltage Output. This pin provides the Negative Reference Voltage used by the 16-bit modem converters and the 16-bits telephony converters, and should be externally decoupled with respect to V<sub>CMM</sub>.

23

V<sub>CMM</sub>

O

Modem and Telephony Common Mode Voltage Output. This output pin is the common mode voltage (AV<sub>DDM</sub>-AGNDM)/2. This output must be decoupled with respect to GND.

#

# PIN DESCRIPTION (continued)

| Pin N°         | Symbol                                              | Type  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|-----------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Symbol                                              | Туре  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MODEM          | AND TELE                                            | PHONY | CODEC (13 pins) (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 29             | TP1Tx+                                              | 0     | Modem #1 Differential Positive Output. This pin is the noninverting output of the fully differential transmit output modem #1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 30             | TP1Tx-                                              | 0     | Modem #1 Differential Negative Output. This pin is the inverting output of the fully differential transmit output modem #1. Outputs TP1Tx+ and TP1Tx- provide analog signals with maximum peak-to-peak amplitude 2 x $V_{REFM}$ , and must be followed by an external two pole smoothing filter. The external filter follows the internal single pole switch capacitor filter with cut-off frequency of 2 x FSM. The cut-off frequency of the external filter must be greater than two times the sampling frequency (FSM), so that the combined frequency response of both the internal and external filters is flat in the band-pass. |

| 27             | TP1Rx+                                              | I     | Modem #1 Differential Positive Analog Input. This pin is the differential non-inverting ADC input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 28             | TP1Rx-                                              | I     | Modem #1 Differential Negative Analog Input. This pin is the differential inverting receive input. The analog input peak-to-peak differential signal range must be less than 2 x V <sub>REFM</sub> , and must be preceeded by an external single pole anti-aliasing filter. The cut-off frequency of the filter must be lower than one half the over-sampling frequency. These filters should be set as close as possible to the TP1Rx+ (TP1Rx-) pins.                                                                                                                                                                                 |

| 31             | TP1Tx2<br>(LQ1)                                     | Ο     | Modem #1 Auxiliary Analog Output or left channel output in quadraphonic mode (LQ1). This pin is the single-ended auxillary modem output. This output provides analog signals with maximum peak-to-peak amplitude $V_{\text{REFM}}$ , and must be followed by an external two pole smoothing filter. The external filter follows the internal single pole switch capacitor filter. The cut-off frequency of the external filter must be greater than two times the sampling frequency (FSM), so that the combined frequency response of both the internal and external filters is flat in the band-pass.                                |

| 34<br>33<br>32 | HandTx1,<br>HandTx2,<br>HandTx3<br>(TP2Tx)<br>(RQ1) | 0     | Telephony Single-ended Outputs or right channel output in quadraphonic mode for TP2Tx (RQ1). These pins are the single-ended outputs of the analog smoothing filter. With maximum peak-to-peak amplitude $V_{REFM}$ , and must be followed by an external two pole smoothing filter. The external filter follows the internal single pole switch capacitor filter. The cut-off frequency of the external filter must be greater than two times the sampling frequency (FSM), so that the combined frequency response of both the internal and external filters is flat in the band-pass.                                               |

| 26<br>22       | HandRx<br>TP2Rx                                     | I     | Telephony Single-ended Input. These pins are the single-ended Telephony ADC input. The analog input peak-to-peak single-ended signal range must be less than $V_{REFM}$ , and must be preceeded by an external single pole anti-aliasing filter. The cut-off frequency of the filter must be lower than one half the over-sampling frequency. These filters should be set as close as possible to the TP2Rx, HandRx pins.                                                                                                                                                                                                              |

#### HOST INTERFACE (25 pins)

|    |        |   | ed for Stereo Audio Codec.<br>synchronous with the audio sampling frequency (FSA).                                                                                                                                                                                                                                                                                     |

|----|--------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61 | SIN1   | Ι | Data In. Digital audio data to the DACs, control information, GPIO data are received by the STLC7549 via SIN1. Refer to "Serial Interface Bit Definition" on Page 21.                                                                                                                                                                                                  |

| 60 | SOUT1  | 0 | Data Out. Digital audio data from the ADCs, status information, GPIO data are output from the STLC7549 via SOUT1. Refer to "Serial Interface Bit Definition" on Page 21.                                                                                                                                                                                               |

| 59 | SCLK1  | 0 | Serial Port #1 Bit Clock Output. Clocks the digital data into SIN1 and out of SOUT1 during the frame synchronization interval. The Serial bit clock is generated internally and is equal to the audio Master clock signal frequency MCLKA/(4 x N) where N depends on index register 20 contents.                                                                       |

| 58 | FSYNC1 | 0 | Serial Port #1 Frame Synchronization Output. The frame synchronization signal is used to indicate that the device is ready to send and receive data. The data transfer begins on the falling edge of the frame-sync signal. The frame-sync is generated internally and goes low on the rising edge of SCLK1. FSYNC1 and FSA have the same frequency.                   |

| 55 | MCLKA  | I | Master Clock A for Audio Codec. Master clock input for audio codecs. This signal is the oversampling clock of the DA and AD convertor. It also provides all the clocks of the audio serial interface #1. This input must be driven by a signal with a frequency from 6.144MHz to 12.288MHz. In quadraphonic mode this input provide all Codecs clocks of the STLC7549. |

# PIN DESCRIPTION (continued)

| Pin N°                | Symbol                                 | Туре                    | Function                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|----------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOST IN               | TERFACE (25 p                          | oins) (con              | tinued)                                                                                                                                                                                                                                                                                                                                                                                                       |

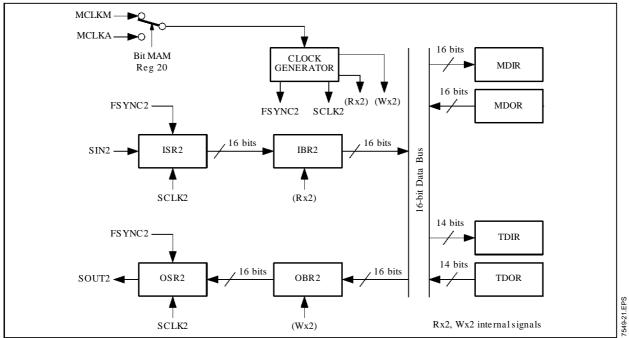

| Serial In<br>The seri | iterface #2 Dedic<br>ial modem interfa | cated for<br>ace is syr | Modem and Telephony Codecs.<br>achronous with the modem sampling frequency (FSM).                                                                                                                                                                                                                                                                                                                             |

| 54                    | SIN2                                   | I                       | Data Input. Digital modem and telephony data to the DACs are received by the STLC7549 via SIN2.                                                                                                                                                                                                                                                                                                               |

| 53                    | SOUT2                                  | 0                       | Data Output. Digital modem and telephony data from the ADCs are output from the STLC7549 via SOUT2.                                                                                                                                                                                                                                                                                                           |

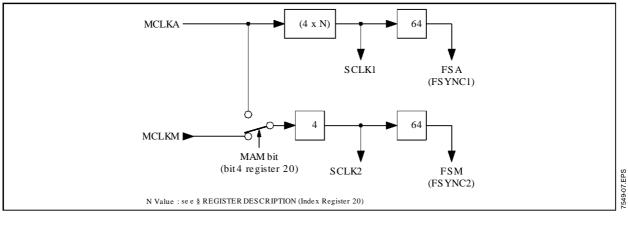

| 52                    | SCLK2                                  | 0                       | Serial Port #2 Bit Clock Output. Clocks the digital data into SIN2 and out of SOUT2 during the frame synchronization interval. The Serial bit clock is generated internally and equal to the Master clock signal frequency MCLKM/4. In quadraphonic mode SCLK2 is equal to MCLKA/4 (refer to Figure 4).                                                                                                       |

| 51                    | FSYNC2                                 | 0                       | Serial Port #2 Frame Synchronization Output. The frame synchronization signal is used to indicate that the device is ready to send and receive data. The data transfer begins on the falling edge of the frame-sync signal. The frame-sync is generated internally and goes low on the rising edge of SCLK2. FSYNC2 and FSM have the same frequency.                                                          |

| 50                    | MCLKM                                  | I                       | Master Clock M for Modem and Telephony Codecs. Master clock input for modem codecs. In quadraphonic mode this input is ignored. This signal is the oversampling clock of the DA and AD convertor. It also provides all the clocks of the modem serial interface #2. This input may be driven by a signal with a frequency from 1.8432MHz to 3.84MHz (up to 11.2896MHz in Quadraphonic mode).                  |

| Miscella              | ineous                                 |                         |                                                                                                                                                                                                                                                                                                                                                                                                               |

| 64                    | RESET                                  | I                       | Reset Function (active low). A reset function to initalize the internal counters and control register. A minimum low pulse of 100ns is required to reset the chip. This reset function initiates the serial data communications. The reset function will initialize all the registers to their default value and will put the device in a pre-programmed state. Master clocks are not necessary during RESET. |

| 63                    | PDWN                                   | I                       | Power Down (active low). The Power-Down input powers down the entire chip to $0.5$ mW. When PDWN pin is taken low, the device is powered down such that the existing internally programmed state is maintained and all analog outputs are in high impedance. When PDWN is driven high, full operation resumes. If the PDWN input is not used, it should be tied to V <sub>DD</sub> .                          |

| 62                    | TEST                                   | I                       | Test Input. Digital input reserved for test. Should be connected to GND.                                                                                                                                                                                                                                                                                                                                      |

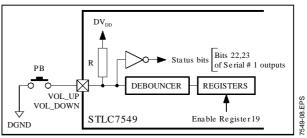

| 39                    | VOL_UP                                 | I                       | Pushbutton Lineout Control Volume UP (edge sensitive, active low, internal pull-up). This pin increases the volume and also affects the left and right gain select values in register 10.                                                                                                                                                                                                                     |

| 38                    | VOL_DOWN                               | I                       | Pushbutton Lineout Control Volume DOWN (edge sensitive, active low, internal pull-up). This pin decreases the volume and also affects the left and right gain select values in the register 10.                                                                                                                                                                                                               |

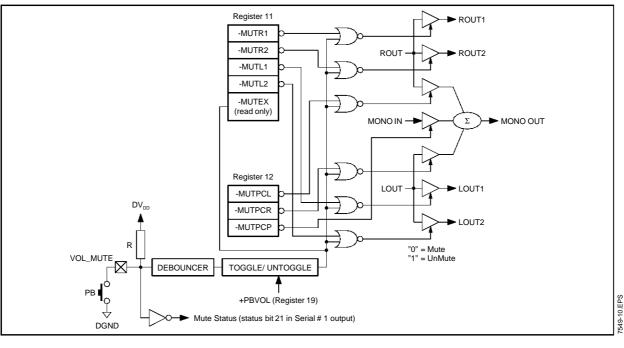

| 37                    | VOL_MUTE                               | I                       | Pushbuttons Lineout Control Volume MUTE (edge sensitive, active low, internal pull-up). This pin mutes and unmutes (toggle function) the Left and Right attenuators overriding the mute bits in registers 11 and 12 (refer to Figure 8).                                                                                                                                                                      |

| 36                    | DC_POT                                 | I                       | DC Potentiometer Control Lineout Volume. An external potentiometer can be attached to this pin to determine a 4-bit value to be used as the main Left/Right output attenuator register value (register 10).                                                                                                                                                                                                   |

| 49 : 42               | GPIO[0:7]                              | I/O                     | General Purpose I/Os. General purpose input/outpu <u>t pins.</u><br>These I/Os are configured as inputs at power-up or RESET.                                                                                                                                                                                                                                                                                 |

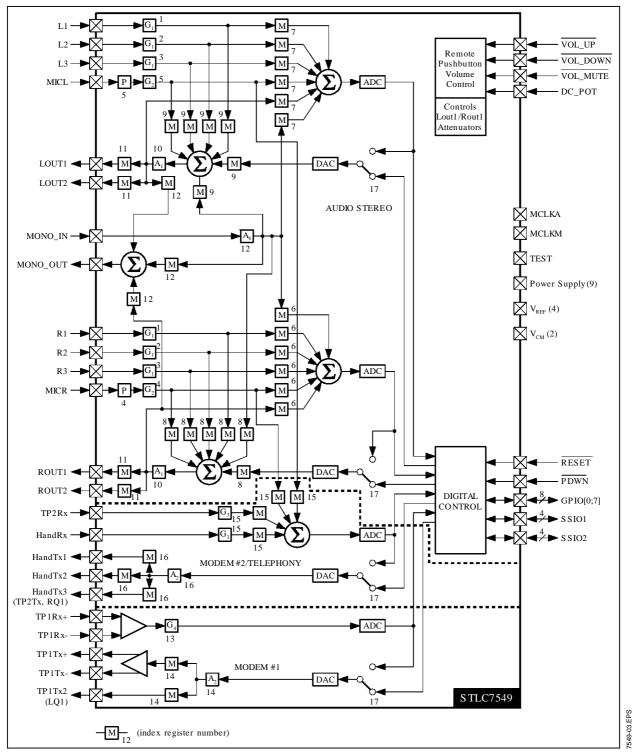

## **BLOCK DIAGRAM**

SGS-THOMSON

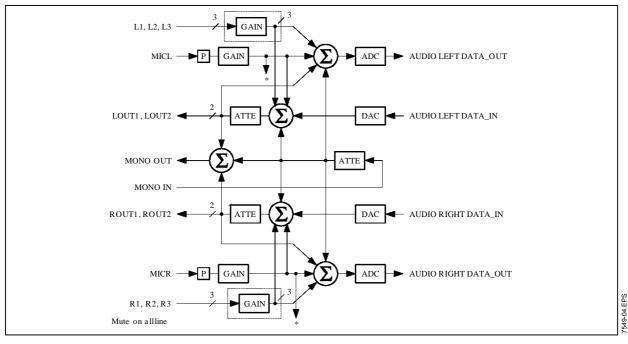

Figure 1 : Simplified Stereo Part Diagram

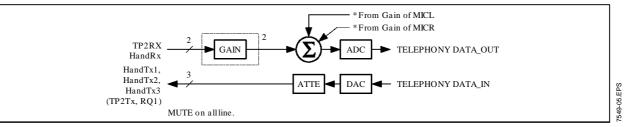

Figure 2 : Simplified Telephony/Modem #2 Part Diagram

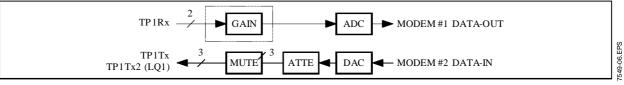

Figure 3 : Simplified Modem #1 Part Diagram

Figure 4 : Clock Generator Diagram

8/30

### FUNCTIONAL DESCRIPTION

#### 1 - Volume Control

The STLC7549 provides a powerful set of volume control functions via pushbuttons (VOL\_MUTE, VOL\_DOWN and VOL\_UP input pins), a potentiometer (DC\_POT input pin) and control registers (Register 10 : Audio line output attenuator control, Register 11 : Audio output mute control, Register 12 : Mono input/output control, Register 19 : digital control Register #1).

#### 1.1 - Index Register 19 : Digital Control Register #1 Description

By setting the bits +PBVOL (pushbutton volume circuitry) or + DCVOL (DC volume control circuitry) the output attenuators will be affected (increment or decrement by 1 LSB the current 4-bit value of volume control Register 10) by the pushbuttons (VOL\_UP,VOL\_DOWN) or by the potentiometer (DC voltage range pin DC\_POT to determine a 4-bit value).

The 4-bit value from the DC potentiometer can be read from Register 19 (bits 4 to 7). If the bits +PBVOL and +DCVOL are both set to "1" the priority is given to +DCVOL.

In pushbutton mode the serial interface is still able to modify the volume setting of Register 10. In potentiometer mode the serial interface can not modify Register 10.

| Index Re | egister 19 | Control Mode                     |                                  |  |

|----------|------------|----------------------------------|----------------------------------|--|

| +PBVOL   | +DCVOL     | VOLUME (1)                       | MUTE (2)                         |  |

| 0        | 0          | Serial Interface                 | Serial Interface                 |  |

| 1        | 0          | Pushbuttons/<br>Serial Interface | Pushbuttons/<br>Serial Interface |  |

| 0        | 1          | Potentiometer                    | Serial Interface                 |  |

| 1        | 1          | Potentiometer                    | Pushbuttons                      |  |

Notes: 1. Register 10 2. Registers 11,12

#### 1.2 - Pushbuttons Circuitry

The pushbuttons volume circuitry (VOL\_MUTE, VOL\_UP and VOL\_DOWN) will affect the main left/right output attenuator in Register 10 and mute blocks in Registers 11,12 and do not mute the PC speaker (Register 12). When switching from serial interface control mode to pushbuttons control mode the contents of the Registers 10,11,12 are kept. If more than 1 pushbutton is pushed, then the priority is given to the one pushed first.

The action on VOL\_UP and VOL\_DOWN pushbuttons will increment or decrement the contents of the left and right output attenuator in Register 10. The status of the input pins are inverted and reflected in bits 21, 22 and 23 of the serial output#1 interface. The input pins are debounced before acting on registers value. The input pins are edge sensitive and active low.

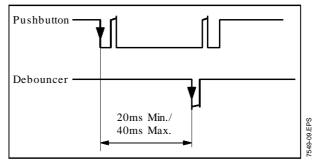

The push-buttons are debounced as shown in Figures 5 and 6. The internal pull-up resistance is over  $20k\Omega$ .

Figure 6

In order to better understand the MUTE pushbutton function please see Figure 8. After RESET the output of the TOGGLE/UNTOGGLE circuitry is in unmute position.

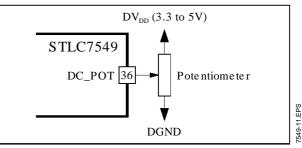

# 1.3 - Potentiometer circuitry

With the internal DC to 4-bit value convertor you can control the output volume just with a simple potentiometer of  $100k\Omega$ . When switched to DC volume control mode, the contents of the volume Register 10 are up-dated with the 4-bit convertor value of the potentiometer circuitry. The 4-bit value volume control register is up-dated at least every 100ms. The potentiometer circuitry has an hysteresis of 1/2 LSB. The DC potentiometer circuitry is shown in Figure 7.

#### Figure 7

#### FUNCTIONAL DESCRIPTION (continued)

#### 2 - Mute Function

The mute function allows each input and output channel to be silenced independently. This function maintains the configuration (gain, attenuation, mixing configuration) during the mute and unmute. The output channels should be muted when the sampling frequency is changed.

For the complete description of the mute possibilities see :

- Register 6 (Right ADC Summer control)

- Register 7 (Left ADC Summer control)

- Register 8 (Right DAC Summer control)

- Register 9 (Left DAC Summer control)

- Register 11 (Audio output Mute control)

- Register 12 (Mono Input/Output control)

- Register 14 (Mono codec#1 output control)

- Register 15 (Mono codec#2 input control)

- Register 16 (Mono codec#2 output control)

#### 3 - Input Gain and Output Gain Setting

Both input and output gain setting are internally made on zero crossing of the analog signal to minimize the "zipper" noise. The gain setting on zero crossing of the analog signal is not available in the preamplifier P. The gain change automatically takes effect if zero crossing does not occur within 512 frames. The 512 frames counter is initialized by the register gain access.

#### 4 - Offset Cancellation

The internal input offsets are minimized by internal offset cancellation circuitry. The calibration proce-

Figure 8 : Mute Function

dure is forced by setting bit 0 or bit 1 of Register 19 to "1". The lengh of time required for calibration is 1024 samples at the sampling frequency rate (eg: FSx = 44.1 kHz, T = 1024 \* 1/FSx = 23 ms). When calibration is completed the bit 0 or bit 1 of Register 19 is reset to "0". During calibration the analog inputs are set to a high impedance state and the data value at SOUT are not valid.

#### 5 - Quadraphonic Mode

The STLC7549 offers the possibility to play music in quadraphonic mode. This mode will allow you to power your multimedia application by providing surround sound using RQ1 (Right Quadraphonic 1 output) and LQ1 (Left Quadraphonic 1 output) along with the normal stereo outputs Lout1 and Rout1.

This mode is programmed by setting the bit MAM (Modem Audio Mode, Register 20) to "1", this will cause the modem codecs #1 and #2 clocks to be controlled from the audio master clock MCLKA (11.2896MHz). The modem master clock MCLKM will be ignored (see CLOCK GENERATOR DIA-GRAM) (Figure 4).

In this mode the FSA must be programmed to 44.1kHz (NDIV1 and NDIV0 of Register 20 equals zero so N=1). FSM will be equal to MCLKA/4/64 = 44.1kHz.

For Quadraphonic mode you will have also to program the bit MOR (Modem Oversampling Ratio, Register 20) to "1" so the oversampling ratio will be 128.

SGS-THOMSON

#### FUNCTIONAL DESCRIPTION (continued)

#### 6 - Analog Inputs and Outputs

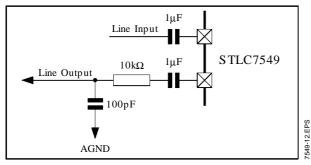

Figure 9 illustrates the suggested connection to obtain full performance from the STLC7549. Any unused analog input should be tied to  $V_{CM}$  directly.

### Figure 9

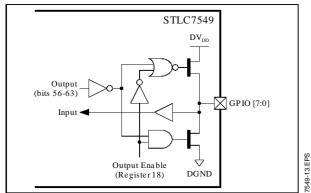

# 7 - General Purpose Input/Output : GPIO [7:0]

The STLC7549 offers 8 general purpose Input/Output pins. The setting of the GPIO configuration is done through Register 18 (bit set to "0" for input configuration and bit set to "1" for output configuration). On RESET the pins are configured as Input. The GPIO value is reflected in the serial data stream SOUT1 bits 24-31 (eg : could be used for Ring detect in modem application). When programmed as output the GPIO provides the way to control external devices using bits in the serial data input stream SIN1 bits 56-63 (eg: could be used for controlling relay drivers) .The GPIO input voltage is independant of DV<sub>DD</sub> and can be from 3.3V to 5V.

# Figure 10

#### 8 - Clock Generator

From the Master Clock Audio (MCLKA) and Master Clock Modem (MCLKM) the internal clock generator provides all the synchronous serial interface clocks (SCLK1, FSYNC1, SCLK2 and FSYNC2).

The internal sampling frequency (FSA, FSM) used for A/D and D/A conversion are equal to the synchronous frequency (FSYNC1 and FSYNC2 respectively). FSx and FSYNCx frequencies are not in phase.

In Quadraphonicmode the MCLKM input is ignored and the reference master clock is MCLKA. For proper operation the N divider (Register 20) must be set to 1 in order to have FSA and FSM equals.

The modem codecs can run with master clock higher than 3.84MHz (e.g. : 11.2896MHz) but with reduced performances.

# 9 - Reset and Power Down

The reset function initializes the internal counters and control registers. A minimum low pulse of 100ns is required to reset the chip. This reset function initiates the serial data communication. During reset operation the SCLKx, FSYNCx and SOUTx output are driven high.

After a reset :

- the registers are set to a known value (refer to register description)

- the GPIO [0:7] are set to Input configuration.

- the output of TOGGLE/UNTOGGLE mute function is placed in unmute state.

- all the internal data paths are set to "0".

- the calibrations of all converters are lost.

The  $\overrightarrow{PDWN}$  input powers down the entire chip. Minimum power consumption is obtained when the MCLKx are stopped. When PDWN pin is taken low the device powers down such that the existing programmed state is maintained and all analog outputs are in a high impedance state. In power down mode the Vcmx is floating. When power down is driven high full operation resumes. If the power down input is not used, it should be tied to  $DV_{DD}$ .

The STLC7549 provides also 3 software power down modes detailed in Register 20.

#### FUNCTIONAL DESCRIPTION (continued)

#### 10 - Voltage Decoupling

To obtain published performance , the analog AV<sub>DD</sub>, digital  $DV_{DD}$  and common mode voltage VCMM (VCMA) should be decoupled with respect to AGND for AV<sub>DD</sub> and VCMM(VCMA) and to DGND for DV<sub>DD</sub>. The decoupling is intented to

#### Figure 11

isolate digital noise from the analog section. Decoupling capacitors should be as close as possible to the voltage pin.

All the ground pins must be tied together (see following schematics).

# **ELECTRICAL SPECIFICATION**

Unless otherwise noted, Electrical Characteristics are specified over the operating range. Typical values are given for  $V_{DD} = +5V$ ,  $T_{amb} = 25^{\circ}C$  and for nominal master clocks frequency MCLKA = 11.2896MHz and MCLKM = 2.4576MHz.

| Symbol            | Parameter                                   | Value                        | Unit |

|-------------------|---------------------------------------------|------------------------------|------|

| $AV_{DD}$         | Analog Power Supply                         | -0.3, 6.0                    | V    |

| $DV_DD$           | Digital Power Supply                        | -0.3, 6.0                    | V    |

| lı                | Input Current per Pin (except supply pins)  | -10, 10                      | mA   |

| lo                | Output Current per Pin (except supply pins) | ±20                          | mA   |

| VIA               | Analog Input Voltage                        | -0.3, AV <sub>DD</sub> + 0.3 | V    |

| VID               | Digital Input Voltage                       | -0.3, DV <sub>DD</sub> + 0.3 | V    |

| VIDGPIO           | Digital Input Voltage at GPI/O              | 5.25                         | V    |

| T <sub>oper</sub> | Operating Temperature                       | 0, +70                       | °C   |

| T <sub>stg</sub>  | Storage Temperature                         | -40, +125                    | °C   |

| P <sub>DMAX</sub> | Maximum Power Dissipation                   | 1500                         | mW   |

Warning: Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

### **RECOMMENDED OPERATING CONDITIONS** (AGND = DGND = 0V, all voltages with respect to 0V)

| Symbol             | Parameter                                                               | Min.                    | Тур.        | Max.                    | Unit |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------|-------------------------|-------------|-------------------------|------|--|--|--|--|--|

| SINGLE PC          | SINGLE POWER SUPPLY ( $DV_{DD} = AV_{DD}$ )                             |                         |             |                         |      |  |  |  |  |  |

| V <sub>DD</sub>    | Supply Voltage                                                          | 4.75                    | 5           | 5.25                    | V    |  |  |  |  |  |

| ID                 | Digital Supply Current                                                  |                         | 95          |                         | mA   |  |  |  |  |  |

| I <sub>A</sub>     | Analog Supply Current                                                   |                         | 55          |                         | mA   |  |  |  |  |  |

| I <sub>LPH</sub>   | Supply_Current in Low Power Hardware Mode<br>(PDWN = "0") (MCLKs stops) |                         | 10          |                         | μA   |  |  |  |  |  |

| I <sub>LPSW1</sub> | Supply Current in Low Power Software Mode 1 (see Register 20)           |                         | TBD         |                         | μΑ   |  |  |  |  |  |

| ILPSW2             | Supply Current in Low Power Software Mode 2                             |                         | TBD         |                         | μΑ   |  |  |  |  |  |

| I <sub>LPSW3</sub> | Supply Current in Low Power Software Mode 3                             |                         | TBD         |                         | μΑ   |  |  |  |  |  |

| PD                 | Power Dissipation                                                       |                         | 750         |                         | mW   |  |  |  |  |  |

| V <sub>CM</sub>    | Common Mode Voltage Output                                              | AV <sub>DD</sub> /2 -5% | $AV_{DD}/2$ | AV <sub>DD</sub> /2 +5% | V    |  |  |  |  |  |

DUAL POWER SUPPLY (DV<sub>DD</sub> # AV<sub>DD</sub>)

|                    | ( 22 22)                                                                       |                         |                     |                         |    |

|--------------------|--------------------------------------------------------------------------------|-------------------------|---------------------|-------------------------|----|

| $DV_{DD}$          | Digital Supply Voltage                                                         | 3.15                    | 3.3                 | 3.45                    | V  |

| ID                 | Digital Supply Current                                                         |                         | 50                  |                         | mA |

| $AV_{DD}$          | Analog Supply Voltage                                                          | 4.75                    | 5.0                 | 5.25                    | V  |

| IA                 | Analog Supply Current                                                          |                         | 55                  |                         | mA |

| I <sub>LPH</sub>   | <u>Supply</u> Current in Low Power Hardware Mode<br>(PDWN = "0") (MCLKs stops) |                         | TBD                 |                         | μΑ |

| I <sub>LPSW1</sub> | Supply Current in Low Power Software Mode 1 (see Register 20)                  |                         | TBD                 |                         | μΑ |

| I <sub>LPSW2</sub> | Supply Current in Low Power Software Mode 2                                    |                         | TBD                 |                         | μA |

| I <sub>LPSW3</sub> | Supply Current in Low Power Software Mode 3                                    |                         | TBD                 |                         | μΑ |

| PD                 | Power Dissipation                                                              |                         | 450                 |                         | mW |

| V <sub>CM</sub>    | Common Mode Voltage Output                                                     | AV <sub>DD</sub> /2 -5% | AV <sub>DD</sub> /2 | AV <sub>DD</sub> /2 +5% | V  |

| ICM                | Common Mode Current Output (see Note 1)                                        |                         | 100                 |                         | μA |

Note 1: DC current only IF dynamic loading exists, than the common mode voltage output must be buffered or the performance of ADCs and DACs will be degraded

#### AUDIO

$\begin{array}{l} AV_{DD}=5V,\,DV_{DD}=3.3V\ ;\ Input \ Ievels:\ Logic\ 0=0V,\ Logic\ 1=DV_{DD}\ ;\\ 1kHz\ input\ sine\ wave\ ;\ Conversion\ rate\ =44.1kHz\ ;\\ Measurement\ bandwidth\ is\ 20Hz\ to\ 20kHz,\ 16-bit\ Iinear\ coding\ for\ audio,\ microphone\ inputs.\\ Gain\ setting\ and\ Attenuation\ (0dB)\ ;\ 0dBr\ =1V_{RMS}\ (sine\ wave)\ ;\ Load\ impedance\ 10k\Omega,\ 20pF\ ;\\ Unless\ otherwise\ specified. \end{array}$

#### **Analog Input Characteristics**

| Symbol          | Parameter                                              |                                           | Min.         | Тур.       | Max.         | Unit       |

|-----------------|--------------------------------------------------------|-------------------------------------------|--------------|------------|--------------|------------|

| ADR             | ADC Resolution                                         |                                           | 16           |            |              | Bits       |

| DNL             | ADC Differential Nonlinearity (see Note 2              | 1)                                        | -0.9         |            | +0.9         | LSB        |

| SID             | Signal to Intermodulation Distortion                   |                                           |              | 85         |              | dB         |

| lcl             | Interchannel Isolation (f = 1kHz, Vinput = 2           | 200mVpp)                                  | 85           |            |              | dB         |

| IcGM            | Interchannel Gain Mismatch                             | Line Inputs<br>Microphone Inputs          | -0.5<br>-0.5 |            | +0.5<br>+0.5 | dB<br>dB   |

| PIGS            | Programmable Input Gain Span                           | Line Inputs<br>Microphone Inputs          | 28<br>55.5   | 30<br>57.5 | 32<br>59.5   | dB<br>dB   |

| GSEr            | Gain Step Size Error (see Note 3)                      | Line Inputs<br>Microphone Inputs          |              |            | 0.5<br>0.5   | dB<br>dB   |

| OFFr            | ADC Offset Error<br>(microphone pre-amplifier at maxim | Line Inputs<br>um gain) Microphone Inputs |              | 10<br>600  | 100<br>1000  | LSB<br>LSB |

| FSI             | Full Scale Input Voltage                               | Line and Microphone Inputs                | 2.8          | 2.9        | 3.0          | Vpp        |

| R <sub>IN</sub> | Input Resistance (see Note 1)                          | Line Inputs<br>Microphone Inputs          | 100<br>10    |            |              | kΩ<br>kΩ   |

| C <sub>IN</sub> | Input Capacitance (see Note 1)                         |                                           |              |            | 15           | pF         |

| SNDR            | Signal / Noise + Distortion at -6dBr ; 1kH             | Iz ADC Audio<br>ADC Micro                 | 79<br>70     |            |              | dB<br>dB   |

| DR              | Dynamic Range (see Note 2)                             |                                           | 85           |            |              | dB         |

#### **Analog Output Characteristics**

| Symbol           | Parameter                                  |           | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------------|-----------|------|------|------|------|

| DAR              | DAC Resolution                             |           | 16   |      |      | Bits |

| DNL              | DAC Differential Nonlinearity (see Note 1) |           | -0.9 |      | +0.9 | LSB  |

| SNDR             | Signal / Noise + Distortion at -10dBr      |           | 75   |      |      | dB   |

| DR               | Dynamic Range (see Note 2)                 |           | 85   |      |      | dB   |

| SID              | Signal to Intermodulation Distortion       |           |      | 85   |      | dB   |

| lcl              | Interchannel Isolation                     | Line Out  | 85   |      |      | dB   |

| IcGM             | Interchannel Gain Mismatch                 | Line Out  | -0.5 | 0.1  | +0.5 | dB   |

| PAS              | DAC Programmable Attenuation Span          |           | 42   | 45   | 48   | dB   |

| ASS              | DAC Attenuation Step Size                  |           | 2.5  | 3    | 3.5  | dB   |

| VOFF             | DAC Offset Voltage                         |           | -100 |      | +100 | mV   |

| FSO              | Full Scale Output Voltage                  |           | 2.8  | 2.9  | 3.0  | Vpp  |

| RL               | Load Resistance                            |           | 10   |      |      | kΩ   |

| CL               | Load Capacitance                           |           |      |      | 20   | pF   |

| R <sub>OUT</sub> | Output Resistance                          |           |      |      | 20   | Ω    |

| MAtt             | Mute Attenuation (0dB gain)                |           | 85   |      |      | dB   |

| OBE              | Total Out-of-band Energy (see Note 1) Fs/2 | to 100kHz |      |      | -45  | dBr  |

Notes: 1. This specification is guaranteed by characterization, not production testing.

2. DR measured over the full bandwidth 0Hz to FSA/2 with -20dBr signal extrapoled to full scale.

3. The gain step size error is the deviation of a gain or attenuation step from a straight line passing through the no-gain/attenuation value and the ideal full-gain/attenuation value.

### MODEM AND TELEPHONY

$AV_{DD} = 5V$ ,  $DV_{DD} = 3.3V$ ; Input levels : Logic 0 = 0V, Logic 1 =  $DV_{DD}$ ; 1kHz input sine wave; Conversion rate = 9.6kHz. Measurement bandwidth is 100Hz to 4800Hz, 16-bit linear coding for modem inputs and 16-bit linear coding for telephony inputs. For quadraphonic mode the measurement are done with MCLKA = 11.2896MHz and MAMbit set to 1 in Register 20. Gain settings and attenuation (0dB); 0dBr = 2 x V<sub>REFM</sub> peak-to-peak; Load impedance 10k $\Omega$ , 20pF; unless otherwise specified.

#### Analog Input Characteristics

| Symbol          | Parameter                                                 |                                                    | Min.       | Тур.                                       | Max.       | Unit           |

|-----------------|-----------------------------------------------------------|----------------------------------------------------|------------|--------------------------------------------|------------|----------------|

| ADR             | ADC Resolution                                            | Modem #1<br>Modem #2                               | 16<br>16   |                                            |            | Bits<br>Bits   |

| DNL             | ADC Differential Nonlinearity (see Note 1)                |                                                    | -0.9       |                                            | +0.9       | LSB            |

| SID             | Signal to Intermodulation Distortion                      |                                                    |            | 85                                         |            | dB             |

| lcl             | Interchannel Isolation (f = 1kHz, V <sub>input</sub> = 20 | 85                                                 |            |                                            | dB         |                |

| PIGS            | Programmable Input Gain Span                              | Modem #1<br>Modem #2                               |            | 6<br>12                                    |            | dB<br>dB       |

| GSEr            | Gain Step Size Error (see Note 3)                         |                                                    |            |                                            | 0.5        | dB             |

| OFFr            | ADC Offset Error                                          | Modem #1<br>Modem #2                               |            | 10<br>10                                   | 100<br>100 | LSB<br>LSB     |

| VREFM           | Differential Reference Voltage Output = V <sub>F</sub>    | REFPM - VREFNM                                     | 2.4        | 2.5                                        | 2.6        | V              |

| FSI             | Full Scale Input Voltage                                  | Modem #1 (differential)<br>Modem #2 (single-ended) |            | 2 x V <sub>REFM</sub><br>V <sub>REFM</sub> |            | V<br>V         |

| R <sub>IN</sub> | Input Resistance                                          | Modem #1<br>Modem #2                               | 100<br>100 |                                            |            | kΩ<br>kΩ       |

| CIN             | Input Capacitance                                         |                                                    |            | 15                                         |            | pF             |

| SNDR            | Signal / Noise + Distorsion at -6dBr ; 1kHz               | Modem #1<br>Modem #2<br>Quadraphonic Mode          |            | 84<br>79<br>70                             |            | dB<br>dB<br>dB |

| DR              | Dynamic Range (see Note 2)                                | Modem #1<br>Modem #2<br>Quadraphonic Mode          |            | 90<br>85<br>76                             |            | dB<br>dB<br>dB |

**Notes :** 1. This specification is guaranteed by characterization, not production testing.

2. DR measured over the full bandwidth 0Hz to FSA/2 with -20dBr signal extrapoled to full scale.

3. The gain step size error is the deviation of a gain or attenuation step from a straight line passing through the no-gain/attenuation value and the ideal full-gain/attenuation value.

# MODEM AND TELEPHONY (continued)

### **Analog Output Characteristics**

| Symbol | Parameter                                                                                                            | Min.     | Тур.                           | Max. | Unit           |

|--------|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------|------|----------------|

| DAR    | DAC Resolution Modem #1<br>Modem #2                                                                                  | 16<br>16 |                                |      | Bits<br>Bits   |

| DNL    | DAC Differential Nonlinearity (see Note 1)                                                                           | -0.9     |                                | +0.9 | LSB            |

| SNDR   | Signal / Noise + Distorsion at -6dBr Modem #1<br>Signal / Noise + Distorsion at -10dBr Modem #2<br>Quadraphonic Mode |          | 84<br>75<br>70                 |      | dB<br>dB<br>dB |

| DR     | Dynamic Range (see Note 2) Modem #1<br>Modem #2<br>Quadraphonic Mode                                                 |          | 90<br>85<br>80                 |      | dB<br>dB<br>dB |

| SID    | Signal to Intermodulation Distortion                                                                                 |          | 85                             |      | dB             |

| lcl    | Interchannel Isolation                                                                                               | 85       |                                |      | dB             |

| Gabs   | Absolute Gain at 1kHz                                                                                                | -0.5     | 0                              | +0.5 | dB             |

| PAS    | DAC Programmable Attenuation Span Modem #1<br>Modem #2                                                               |          | 6<br>6                         |      | dB<br>dB       |

| VOFF   | DAC Offset Voltage                                                                                                   | -100     |                                | 100  | mV             |

| FSO    | Full Scale Output Voltage Modem #1 (differential output)<br>Modem #2 (single ended output)                           |          | 2 x V <sub>REFM</sub><br>Vrefm |      | V<br>V         |

| RL     | Load Resistance                                                                                                      | 10       |                                |      | kΩ             |

| CL     | Load Capacitance                                                                                                     |          |                                | 20   | pF             |

| Rout   | Output Resistance                                                                                                    |          |                                | 20   | Ω              |

| MAtt   | Mute Attenuation                                                                                                     | 85       |                                |      | dB             |

| OBE    | Total Out-of-band Energy (see Note 1) Fs/2 to 100kHz                                                                 |          |                                | -45  | dBr            |

Notes: 1. This specification is guaranteed by characterization, not production testing.

2. DR measured over the full bandwidth 0Hz to FSA/2 with -20dBr signal extrapoled to full scale.

**SWITCHING CHARACTERISTICS** ( $AV_{DD} = DV_{DD} = +5V$ , AGND = DGND = 0V, Outputs loaded with 30pF, Input Levels : Logic 0 = 0V, Logic 1 =  $DV_{DD}$ )

| Symbol                                                                 | Parameter                                                  | Min. | Тур.                         | Max.           | Unit              |

|------------------------------------------------------------------------|------------------------------------------------------------|------|------------------------------|----------------|-------------------|

| MCLKA<br>MCLKM                                                         | Input Clock (MCLKx) Frequency<br>Modem M<br>Quadraphonic M |      | 11.2896<br>2.4576<br>11.2896 | 12.288<br>3.84 | MHz<br>MHz<br>MHz |

| t <sub>PW</sub>                                                        | Master Clock Period                                        |      | 1/MCLKx                      |                | -                 |

| t <sub>PW</sub> /t <sub>CKH</sub><br>t <sub>PW</sub> /t <sub>CKL</sub> | Master Clock (MCLKx) Duty Cycle Pulse Width Pulse Width    |      |                              | 80<br>80       | %<br>%            |

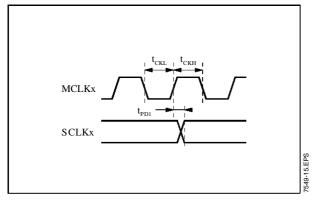

| t <sub>PD1</sub>                                                       | SCLKx Output Delay from MCLKx Rising Edge                  |      |                              | 35             | ns                |

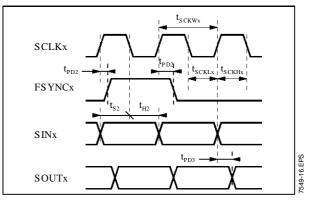

| t <sub>PD2</sub>                                                       | FSYNCx Delay Time                                          |      |                              | 15             | ns                |

| t <sub>S2</sub>                                                        | SINx Set-up Time                                           | 15   |                              |                | ns                |

| t <sub>H2</sub>                                                        | SINx Hold Time from SCLKx Edge                             | 10   |                              |                | ns                |

| t <sub>PD3</sub>                                                       | SOUTx Delay from SCLKx Edge                                |      |                              | 25             | ns                |

| t <sub>SCKW1</sub>                                                     | SCLK 1 Period                                              |      | 1/(64 x FSA)                 |                | s                 |

| tsckH1                                                                 | SCLK 1 High Time                                           | 36   |                              |                | ns                |

| t <sub>SCKL1</sub>                                                     | SCLK 1 Low Time                                            | 36   |                              |                | ns                |

| t <sub>SCKW2</sub>                                                     | SCLK 2 Period Modem M<br>Quadraphonic M                    |      | 1/(64 x FSM)<br>1/(64 x FSA) |                | s<br>s            |

| tsckH2                                                                 | SCLK 2 High Time Modem M<br>Quadraphonic M                 |      |                              |                | ns<br>ns          |

| t <sub>SCKL2</sub>                                                     | SCLK 2 Low Time Modem M<br>Quadraphonic M                  |      |                              |                | ns<br>ns          |

| FSA                                                                    | Audio Sample Frequency (N defined in Reg 20)               |      | MCLKA/ (4 x N x 64)          |                | Hz                |

| FSM                                                                    | Modem & Telephony Sample Frequency                         |      | MCLKM/ (4 x 64)              |                | Hz                |

Figure 12 : SCKLx Output Timing

# DIGITAL FILTER CHARACTERISTICS

| Symbol | Parameter                      | Min.     | Тур. | Max.     | Unit |

|--------|--------------------------------|----------|------|----------|------|

|        | Passband                       | 0        |      | 0.4 x Fs | Hz   |

|        | Abs Gain at 1kHz               | -0.5     |      | +0.5     | dB   |

|        | Passband Ripple (0 - 0.4 x Fs) | -0.2     |      | +0.2     | dB   |

|        | Transition Band                | 0.4 x Fs |      | 0.6 x Fs | Hz   |

|        | Stop Band                      | 0.6 x Fs |      |          | Hz   |

|        | Stop Band Rejection            | 65       |      |          | dB   |

### **DIGITAL CHARACTERISTICS** (AV<sub>DD</sub> = DV<sub>DD</sub> = +5V ; AGND = DGND = 0V)

| Symbol          | Parameter                             | Min.           | Тур. | Max. | Unit                  |    |

|-----------------|---------------------------------------|----------------|------|------|-----------------------|----|

| Vih             | High Level Input Voltage              | Digital Inputs | 2.2  |      | V <sub>DD</sub> + 0.3 | V  |

| VIL             | Low level Input Voltage               |                | -0.3 |      | 0.8                   | V  |

| V <sub>OH</sub> | High Level Output Voltage             | $I_0 = -1mA$   | 2.4  |      | V <sub>DD</sub>       | V  |

| Vol             | Low Level Output Voltage              | $I_0 = 1mA$    |      |      | 0.4                   | V  |

|                 | Input Leakage Current                 | Digital Inputs | -10  | ±1   | 10                    | μA |

| I <sub>OL</sub> | Low Level Output Current (GPIO [0:7]) |                |      |      | 2                     | mA |

#### **INPUT/OUTPUT DESCRIPTION**

### SERIAL INTERFACE

#### Serial Interface Operation

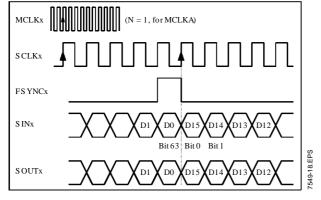

#### Figure 14 : Serial Interface Timing

Serial data input is initiated by a frame synchro signal (FSYNC). The data is clocked from SIN into the input shift register (ISR) on the falling edge of SCLK and transfered to the input buffer register (IBR) when a complete 16-bit word has been received, the register is loaded 8 bits clocks later. Data is assumed to be received MSB first.

Serial data output is initiated by a frame synchro signal (FSYNC). The 16-bit data word is loaded into the output shift register (OSR) and serially clocked out of OSR to SOUT on the rising edge of SCLK.

The data/index register of SOUT1 refer to the index register set of SIN1 within the same frame.

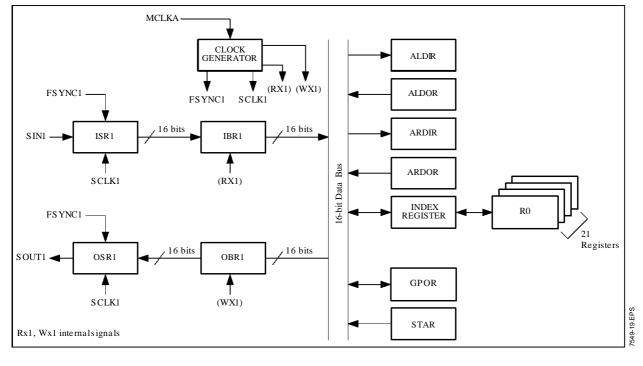

Figure 15 : Audio Serial Interface Block Diagram

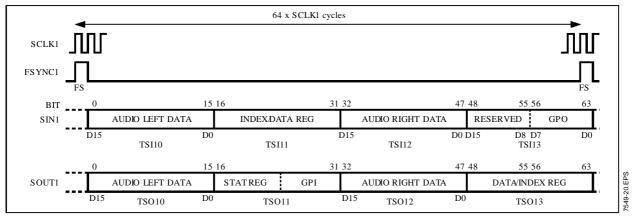

The SCLK is 64 times FSYNC. This mean that the frame contains four slots of 16 bits. The time slots used for circuit function are indicated on the next paragraph.

Serial port 1 and 2

- Frame Synchronization Output (FSYNC)

- Serial Bit Clock Output (SCLK)

- Input Serial Register (ISR)

- Input Buffer Register (IBR)

- Serial Input Data (SIN)

- Output Buffer Register

- Output Serial Register (OSR)

#### Audio Serial Interface One (Figures 15 and 16)

- Audio Left Data Input Register (ALDIR)

- Audio Left Data Output Register (ALDOR)

- Audio Right Data Input Register (ARDIR)

- Audio Right Data Output Register (ARDOR)

- Index Register (R0 to R20)

- General Purpose Output Register (GPOR)

- Status Audio Register

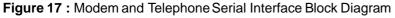

# Modem and Telephone Serial Interface Two (Figures 17 and 18)

- Modem Data Input Register (MDIR)

- Modem Data Output Register (MDOR)

- Telephone Data Input Register (TDIR)

- Telephone Data Output Register (TDOR)

# SERIAL INTERFACE (continued)

#### Figure 16 : Audio Codec Serial Interface (SIO 1) Timing

20/30

# SERIAL INTERFACE BIT DEFINITION

Bit N° Word N°

Definition

# Serial Input #1 Bit Definition (DSP-to-Codec)

| 0 - 15  | 0 | Audio Left DAC Data (16 bits, MSB first)                                                                                                                                                                                                                                  |

|---------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      |   | If = "1", write index register set. If = "0", no write , just read index register set                                                                                                                                                                                     |

| 17      |   | Reserved                                                                                                                                                                                                                                                                  |